The Heartbeat of Modern Technology

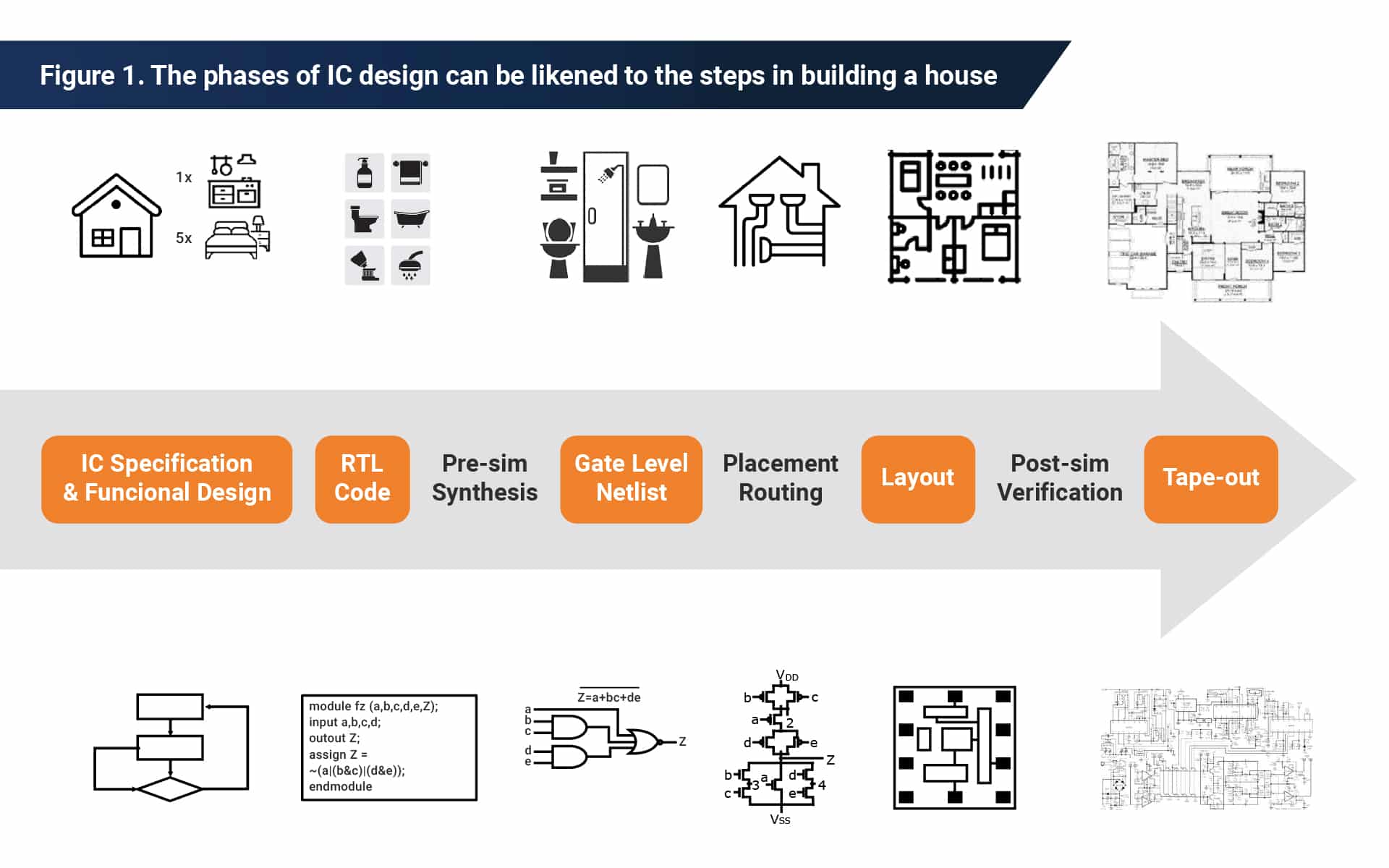

Integrated Circuit (IC) design, often referred to as chip design, is the intricate and highly specialized process of creating the semiconductor chips that power virtually every modern electronic device. From the smartphones in our pockets and the computers on our desks to the sophisticated systems in autonomous vehicles and advanced medical equipment, ICs are the fundamental building blocks of the digital age. At its core, IC design involves conceptualizing, architecting, simulating, verifying, and ultimately manufacturing these complex microelectronic circuits onto a single piece of semiconductor material, typically silicon. This field is a critical nexus of electrical engineering, computer science, and materials science, demanding a deep understanding of physics, logic, and system architecture. The journey from an idea to a functional chip is a multi-stage, iterative process, marked by immense complexity, precision, and innovation.

The Genesis of an Idea: From Concept to Specification

Every IC begins with a need or an improvement. This initial spark is translated into a detailed set of requirements, defining the chip’s intended function, performance metrics, power consumption targets, and physical constraints. This phase is crucial, as a poorly defined specification can lead to costly redesigns later in the development cycle. Engineers will meticulously document every aspect, from the high-level functionality—what the chip is supposed to do—to the granular details of input/output protocols, data processing capabilities, and operational parameters.

Translating Needs into Logic: Functional Specification

The functional specification document serves as the blueprint for the chip’s behavior. It outlines the algorithms to be implemented, the interfaces it will interact with, and the data transformations it will perform. This stage involves a high degree of abstraction, focusing on what the chip needs to achieve rather than how it will be physically realized. Extensive collaboration occurs between system architects, software engineers, and hardware designers to ensure that the specification is comprehensive, unambiguous, and achievable.

Performance, Power, and Area (PPA): The Core Constraints

Beyond functionality, IC design is heavily governed by three critical constraints: Performance, Power, and Area (PPA). Performance dictates how fast the chip can operate and process data. Power consumption is vital for battery-operated devices and for managing heat dissipation in all electronics. Area refers to the physical space the chip occupies on the silicon wafer, which directly impacts manufacturing cost and integration possibilities. Designers must constantly balance these competing demands, often making trade-offs to optimize for the most critical PPA metrics for a given application.

The Architect’s Blueprint: Design and Verification

Once the specification is finalized, the actual design process begins. This is a highly iterative phase where engineers translate the abstract functional requirements into concrete digital logic and physical layouts. The complexity of modern ICs, often containing billions of transistors, necessitates sophisticated Electronic Design Automation (EDA) tools to manage the design flow. Verification is an equally, if not more, critical part of this stage, ensuring that the designed circuit behaves exactly as intended under all possible operating conditions.

Register-Transfer Level (RTL) Design: Building the Logic

The design process typically starts at the Register-Transfer Level (RTL). Here, engineers describe the behavior of the circuit using a Hardware Description Language (HDL) such as Verilog or VHDL. RTL code describes how data flows between registers and the operations performed on that data. This level of abstraction is high enough to describe complex digital systems but detailed enough to be synthesized into a netlist of logic gates. Designers create modules and connect them to form the overall architecture, focusing on the logical operations and data paths.

Hardware Description Languages (HDLs): The Language of Chips

HDLs are specialized programming languages designed to model and describe the behavior and structure of electronic circuits. Verilog and VHDL are the most prevalent, allowing designers to express sequential and combinational logic, state machines, and memory elements. These languages are not imperative programming languages in the traditional sense; rather, they describe the flow of data and signals over time, mirroring the physical behavior of electronic components.

Synthesis: Bridging Logic and Hardware

Following RTL design, the synthesis process takes the HDL code and transforms it into a gate-level netlist. This netlist is a collection of basic logic gates (AND, OR, NOT, flip-flops, etc.) and their interconnections that implement the specified behavior. Synthesis tools use predefined libraries of standard cells provided by semiconductor foundries to perform this conversion. The goal of synthesis is to create a functionally equivalent netlist that also adheres to the PPA constraints.

Logic Synthesis: Optimizing for Performance and Area

Logic synthesis tools analyze the RTL code and systematically map it to the available standard cells. This process involves optimization techniques to minimize gate count (reducing area) and critical path delay (improving performance). Designers often guide the synthesis process through constraints provided in timing constraint files (e.g., Synopsys Design Constraints – SDC), specifying clock frequencies, input/output delays, and other performance targets.

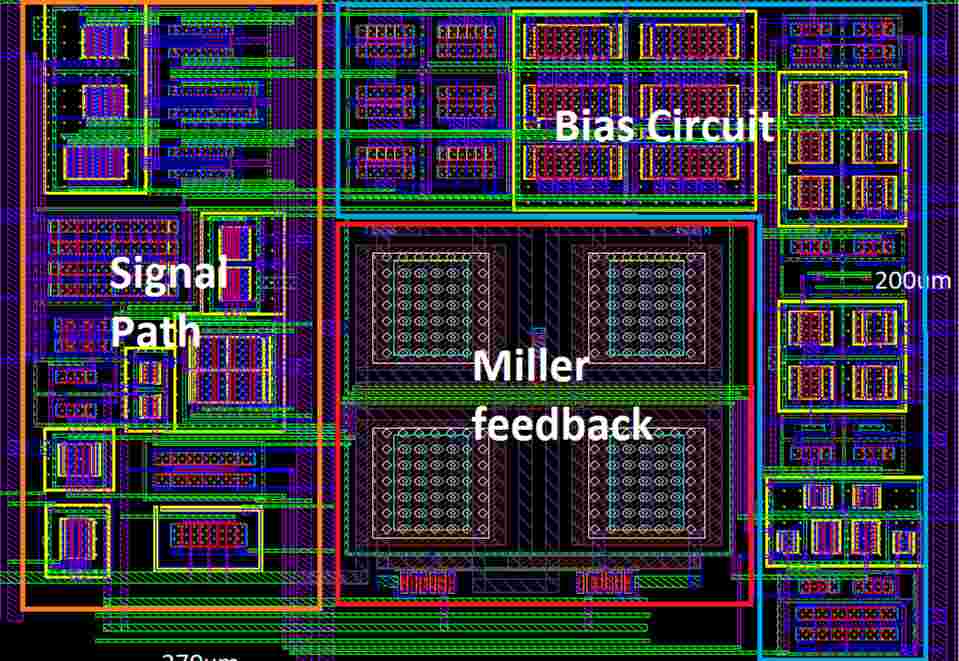

Physical Design: From Gates to Layout

Once a synthesized netlist is obtained, the physical design phase begins. This is where the abstract netlist is translated into a physical layout that can be manufactured. This involves placing the logic gates on the silicon die and routing the interconnections between them. This phase is highly iterative and complex, requiring careful consideration of signal integrity, power delivery, and thermal management.

Placement and Routing: Connecting the Dots

Placement involves determining the optimal location for each standard cell on the silicon die. Good placement significantly impacts the length and complexity of the interconnections, which in turn affects performance and power. Routing then establishes the actual physical connections between these placed cells using multiple layers of metal interconnects. This process must adhere to strict design rules set by the fabrication process to ensure manufacturability.

Verification: Ensuring Correctness and Reliability

Verification is arguably the most time-consuming and critical aspect of IC design. It involves exhaustive testing to ensure that the designed chip functions correctly under all possible conditions and that it meets its performance, power, and area targets. The complexity of modern chips makes exhaustive simulation of all possible scenarios practically impossible, leading to the widespread adoption of advanced verification methodologies.

Simulation: Testing the Design

Simulation is the process of modeling the behavior of the designed circuit and stimulating it with various input vectors to observe its output. Different types of simulators exist, from event-driven simulators that accurately model signal transitions to gate-level simulators used for detailed timing analysis. Designers create testbenches, which are essentially programs that generate stimuli and check the outputs against expected behavior.

Formal Verification: Mathematical Proof of Correctness

Formal verification uses mathematical methods to prove or disprove the correctness of a design without relying on specific test cases. Techniques like model checking and equivalence checking are employed to demonstrate that the design adheres to its specification or that two different representations of the design (e.g., RTL and netlist) are functionally equivalent. This method offers a higher degree of confidence than simulation alone.

Emulation and Prototyping: Real-World Testing

For very complex designs, emulation platforms and field-programmable gate arrays (FPGAs) are used to create hardware prototypes of the chip. These platforms allow for much faster execution of the design than simulation, enabling extensive testing with real-world data and software. This provides a crucial bridge between the simulated world and the actual operational environment.

Manufacturing and Beyond: Bringing the Chip to Life

The culmination of the design and verification process is the creation of manufacturing data, known as GDSII (Graphic Database System II) or OASIS (Open Artwork System Interchange Standard) files. These files contain all the geometric information necessary for a semiconductor fabrication facility (foundry) to produce the actual silicon chips. This involves a highly sophisticated and multi-billion dollar manufacturing process.

Fabrication: The Foundry Process

Fabrication is the process of etching and depositing layers of materials onto a silicon wafer to create the transistors and interconnections that form the IC. This involves a series of hundreds of precise steps, including photolithography, etching, doping, and metallization, performed in highly controlled cleanroom environments. Each layer is meticulously crafted according to the design’s specifications.

Photolithography: Patterning the Layers

Photolithography is a key step where a pattern, derived from the IC design, is transferred onto the silicon wafer using light and masks. Masks, also known as reticles, contain the precise patterns for each layer of the chip. This process defines the intricate geometry of the transistors and wiring.

Wafer Testing: Initial Quality Assurance

Once the wafer has been fabricated, each individual die on the wafer undergoes extensive electrical testing. This wafer sort process identifies functional dies and flags defective ones. Only the functional dies proceed to the next stage.

Packaging and Assembly: From Die to Device

After wafer testing, the functional dies are cut from the wafer and individually packaged. Packaging protects the delicate silicon die from the environment, provides electrical connections to the outside world, and facilitates heat dissipation. This can involve various packaging technologies, from simple leaded packages to complex ball grid arrays (BGAs) and advanced System-in-Package (SiP) solutions.

Assembly: Integrating the Die

The process of attaching the die to the package substrate and connecting it via fine wires or solder balls is known as assembly. This is followed by encapsulation, where the entire structure is sealed to protect it.

Final Testing: The Last Line of Defense

Once packaged, the finished ICs undergo another round of rigorous testing to ensure they meet all performance, power, and functional specifications under various operating conditions. This final test screens out any devices that may have been damaged during the assembly process or that fail to meet the stringent quality standards. Only the fully functional and reliable chips are then shipped to customers for integration into end-user products.

The Ever-Evolving Landscape of IC Design

IC design is a field characterized by relentless innovation. As electronic devices become more powerful, smaller, and more energy-efficient, the demands placed on chip designers grow exponentially. This has led to significant advancements in EDA tools, new transistor architectures, and novel materials. The ongoing drive towards miniaturization, increased functionality, and enhanced performance continues to push the boundaries of what is possible in the realm of integrated circuits, making IC design a pivotal and dynamic area of technological advancement.